Original paper

A 10-bit 100-MS/s Reference-Free SAR ADC in 90 nm CMOS

Volume: 45, Issue: 6, Pages: 1111 - 1121

Published: Jun 1, 2010

Abstract

A 1.2 V 10-bit 100 MS/s Successive Approximation (SA) ADC is presented. The scheme achieves high-speed and low-power operation thanks to the reference-free technique that avoids the static power dissipation of an on-chip reference generator. Moreover, the use of a common-mode based charge recovery switching method reduces the switching energy and improves the conversion linearity. A variable self-timed loop optimizes the reset time of the...

Figures & Tables

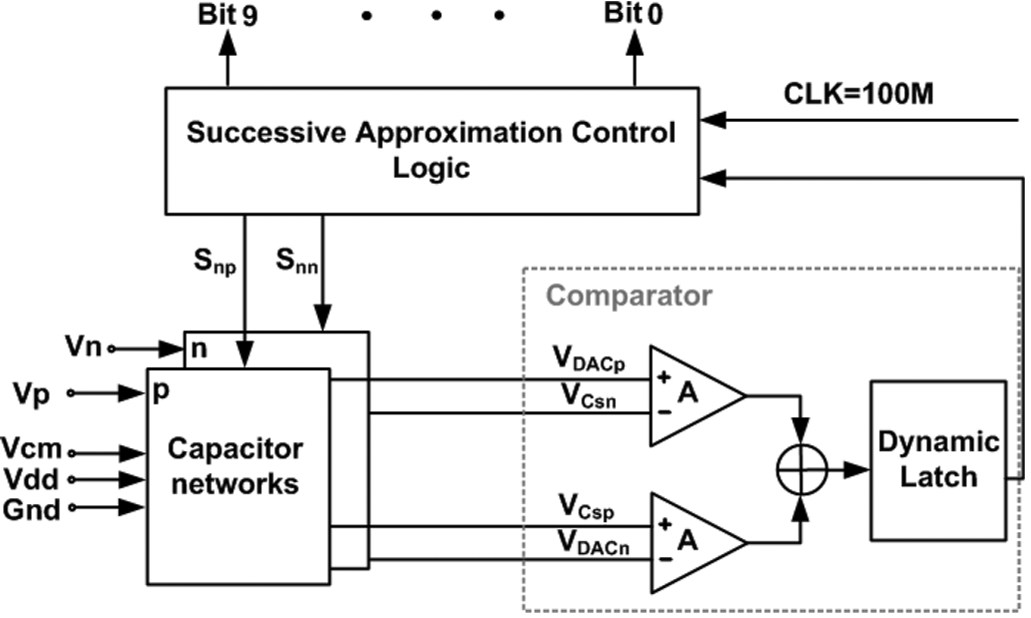

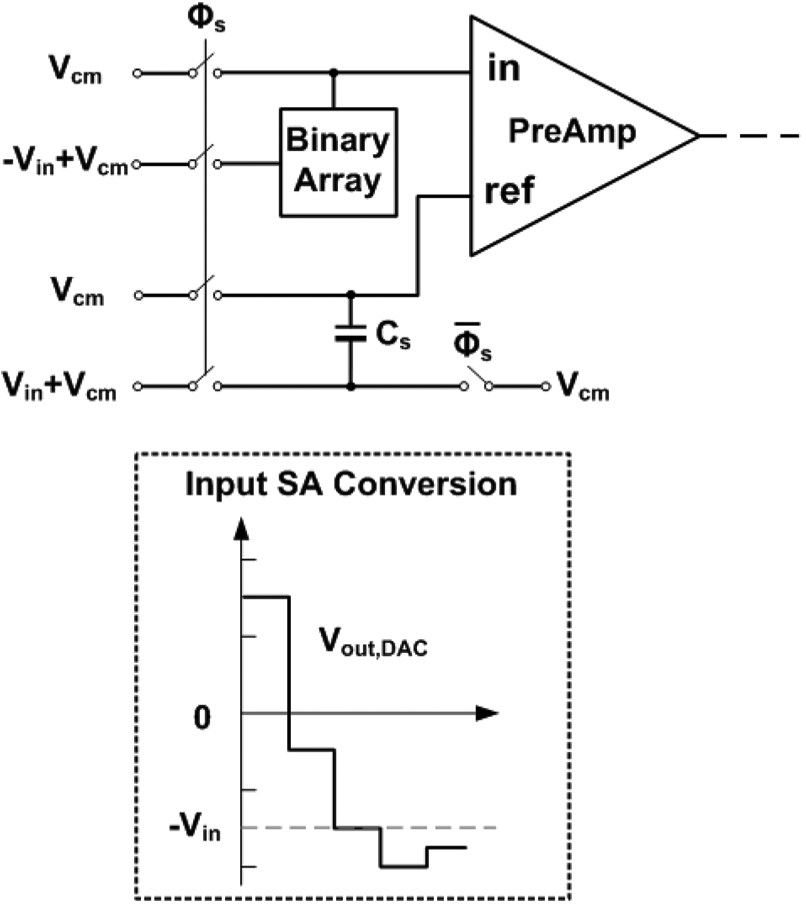

Fig. 1. Overall schematic diagram of the ADC architecture.

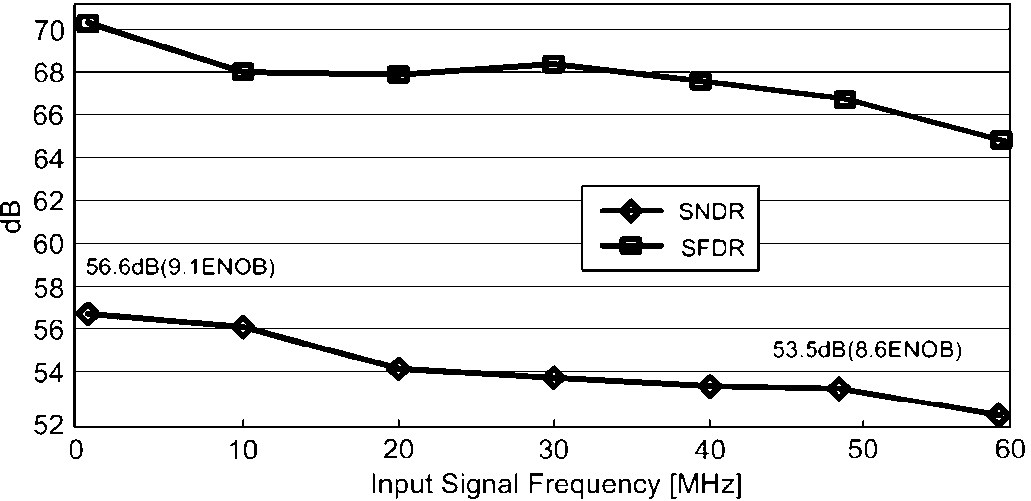

Fig. 10. Dynamic performance versus input frequency.

Fig. 11. FFT of the digital output. The input is either a 1.8 MHz or a 47 MHz si...

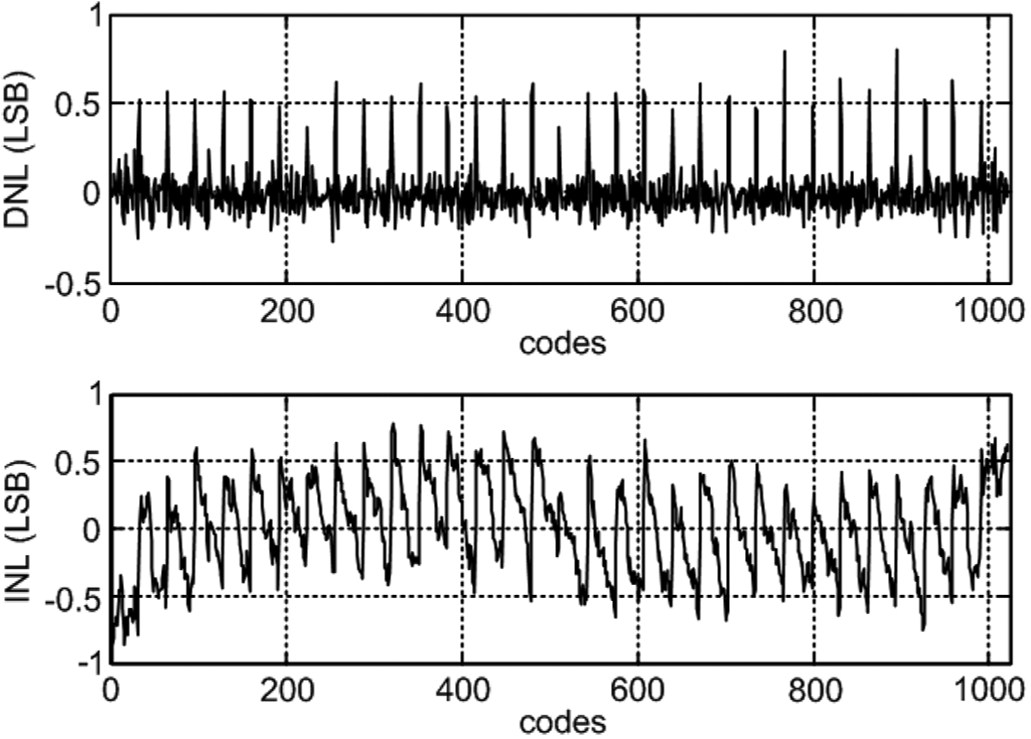

Fig. 12. Measured INL and DNL.

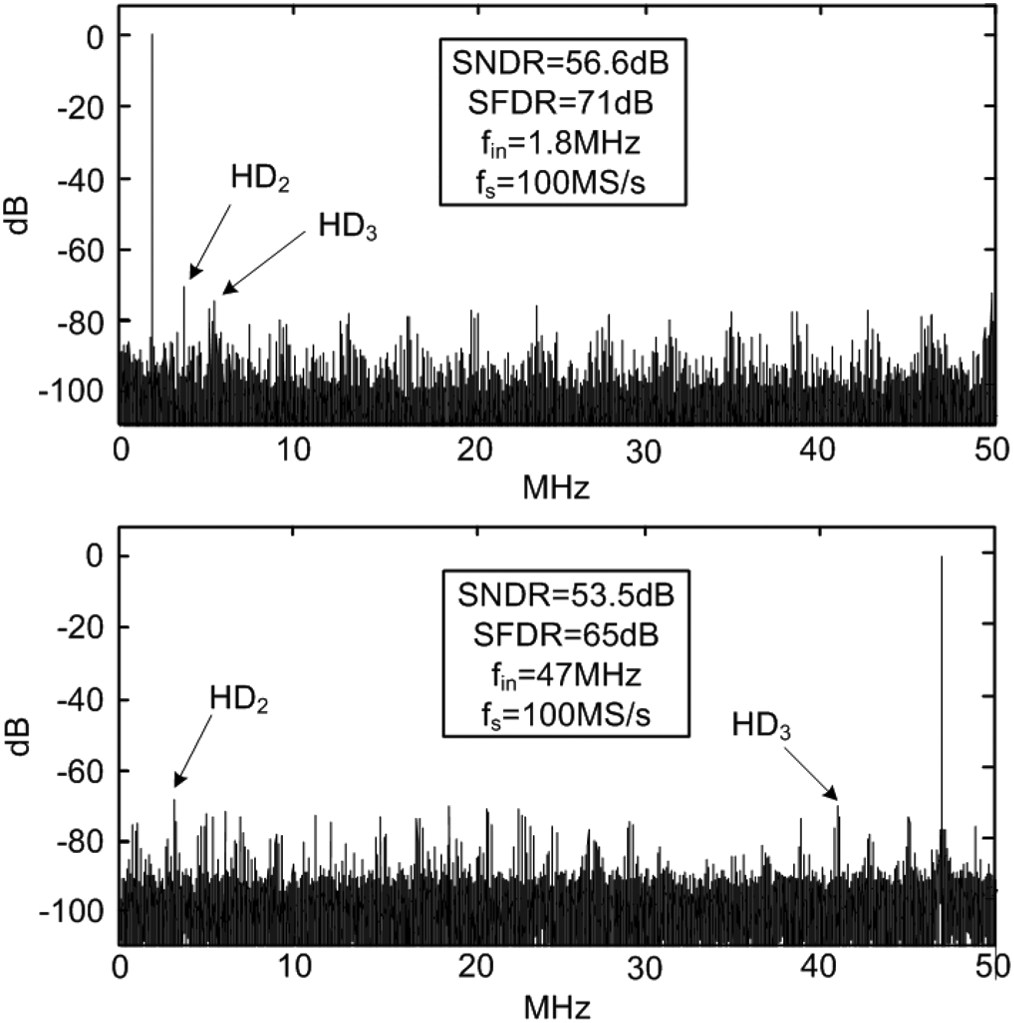

Fig. 2. Conceptual scheme that obtains a passive gain by 2.

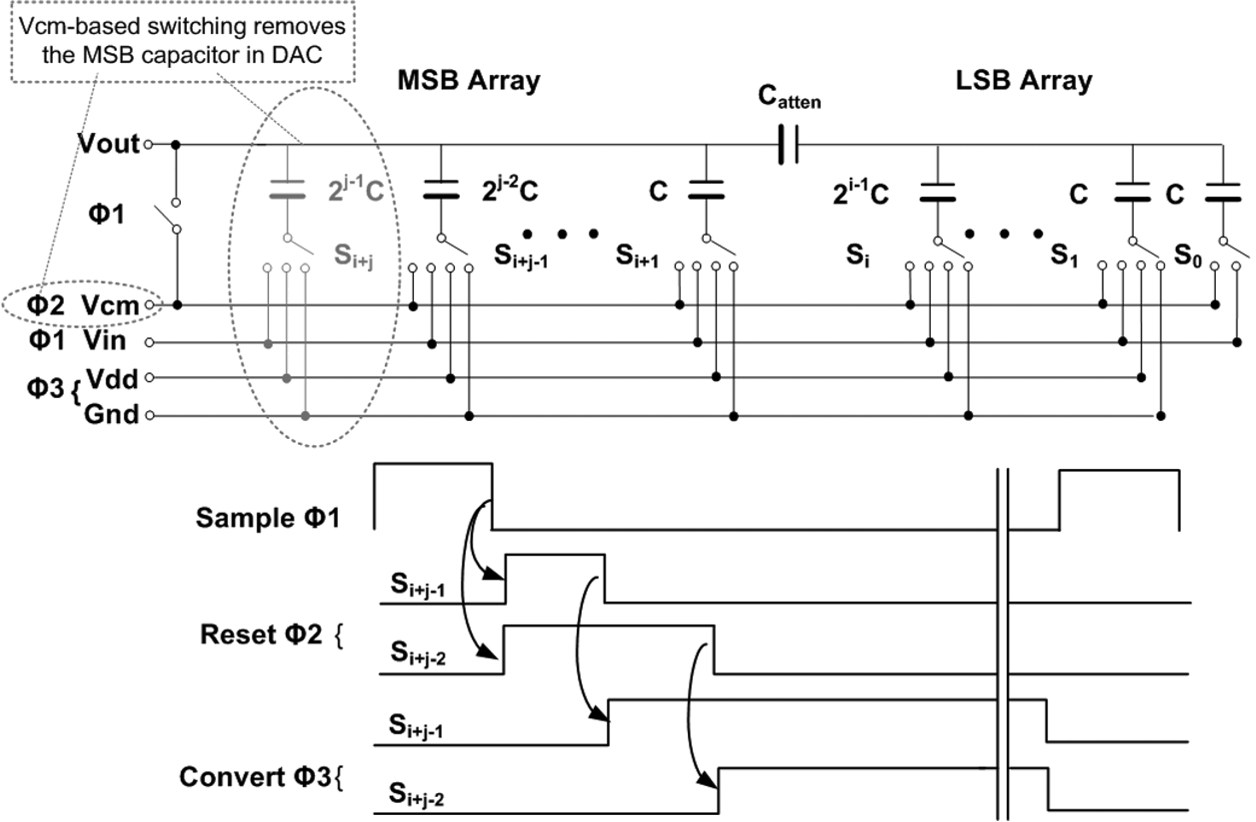

Fig. 3. The -based switching timing diagram with its n-bit split capacitive DAC ...

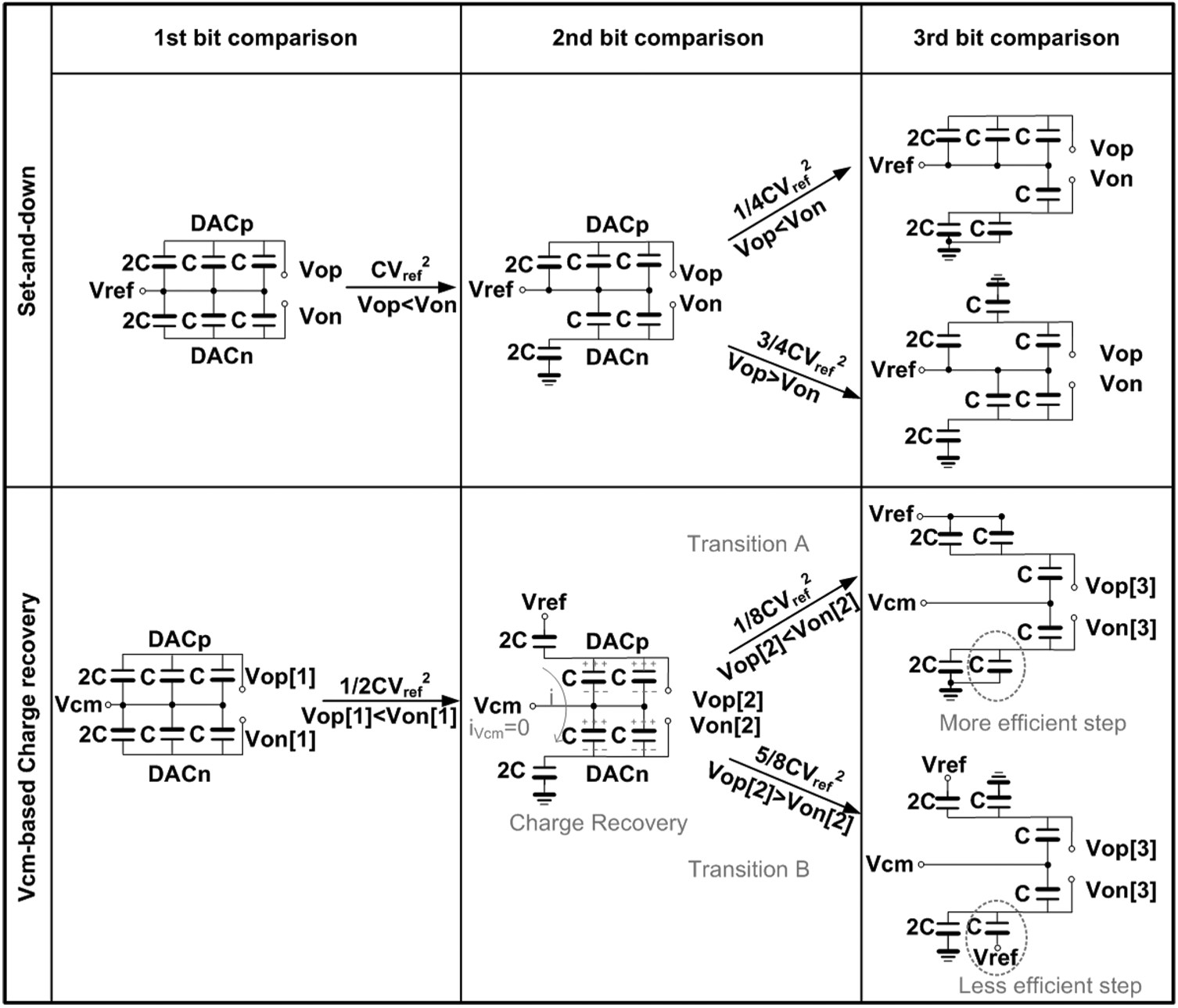

Fig. 4. A 3-bit example of set-and-down and proposed -based switching procedures...

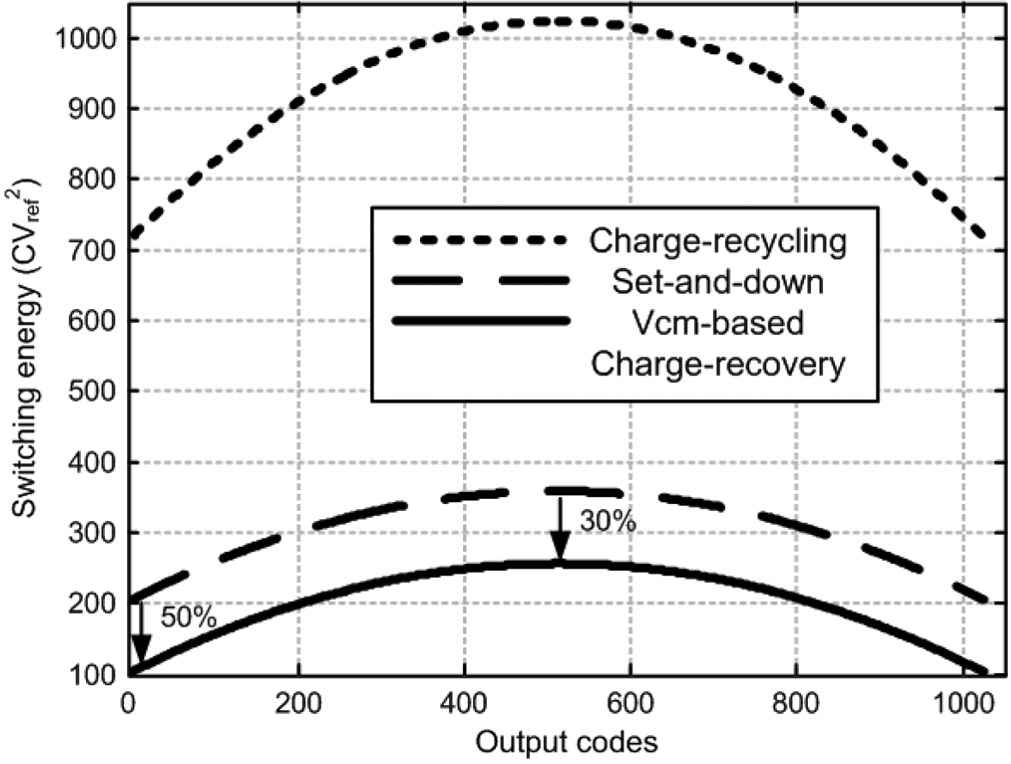

Fig. 5. Switching energy versus output code for three different techniques.

Paper Details

Title

A 10-bit 100-MS/s Reference-Free SAR ADC in 90 nm CMOS

Published Date

Jun 1, 2010

Volume

45

Issue

6

Pages

1111 - 1121

Citation AnalysisPro

You’ll need to upgrade your plan to Pro

Looking to understand the true influence of a researcher’s work across journals & affiliations?

- Scinapse’s Top 10 Citation Journals & Affiliations graph reveals the quality and authenticity of citations received by a paper.

- Discover whether citations have been inflated due to self-citations, or if citations include institutional bias.