Original paper

A 10-bit 50-MS/s SAR ADC With a Monotonic Capacitor Switching Procedure

Volume: 45, Issue: 4, Pages: 731 - 740

Published: Mar 24, 2010

Abstract

This paper presents a low-power 10-bit 50-MS/s successive approximation register (SAR) analog-to-digital converter (ADC) that uses a monotonic capacitor switching procedure. Compared to converters that use the conventional procedure, the average switching energy and total capacitance are reduced by about 81% and 50%, respectively. In the switching procedure, the input common-mode voltage gradually converges to ground. An improved comparator...

Figures & Tables

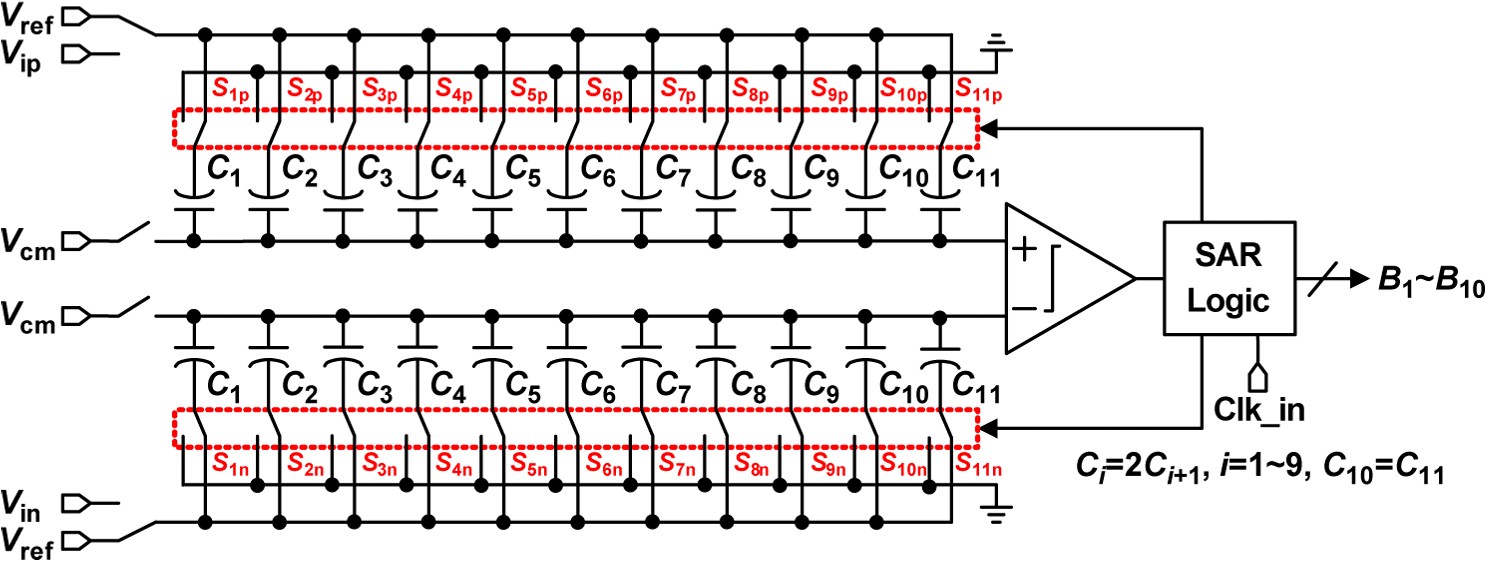

Fig. 1. A conventional 10-bit SAR ADC.

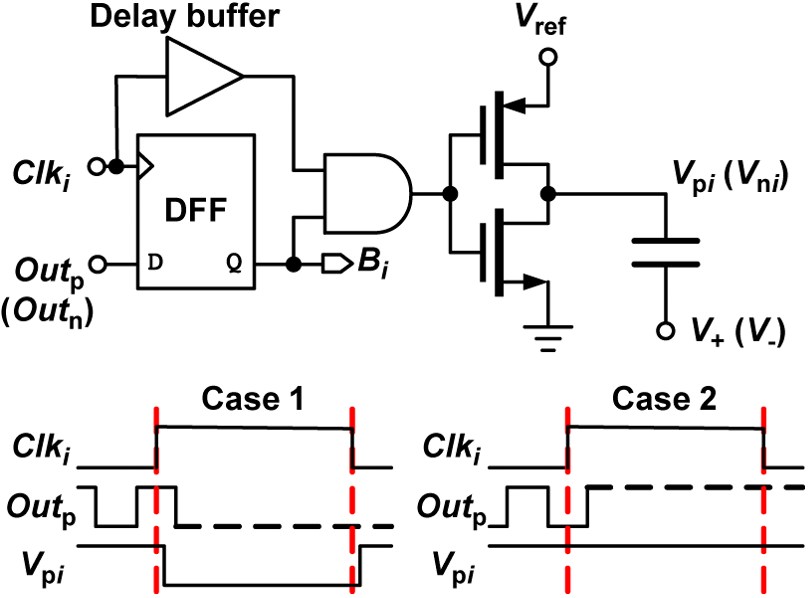

Fig. 10. DAC control logic.

Fig. 11. (a) Sandwich capacitor. (b) Multi-layer sandwich capacitor.

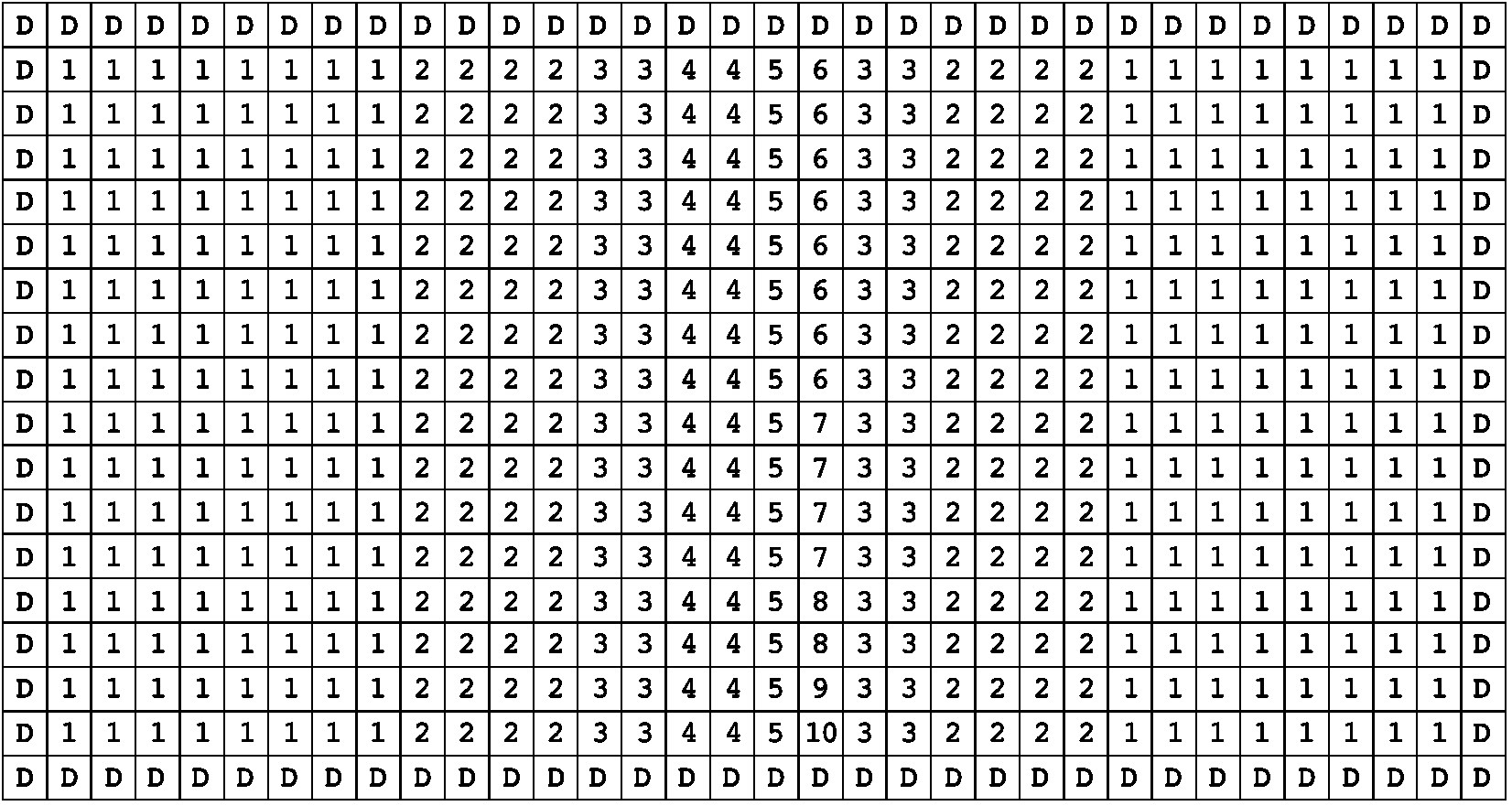

Fig. 12. The layout floorplan of the capacitor array.

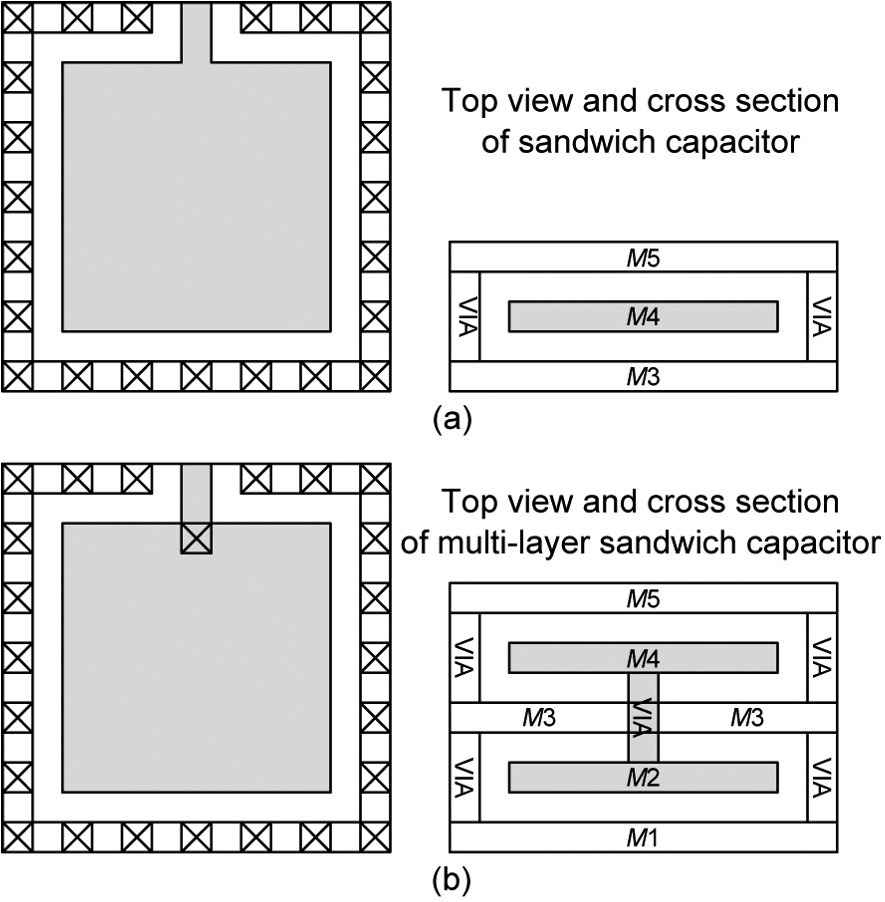

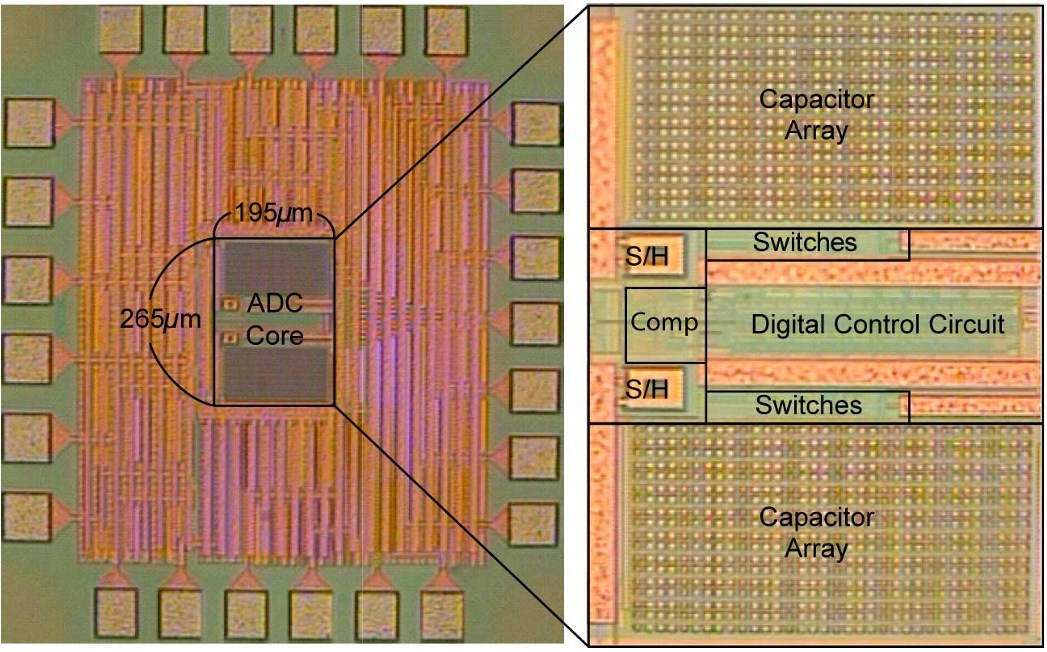

Fig. 13. Die micrograph and the zoomed view.

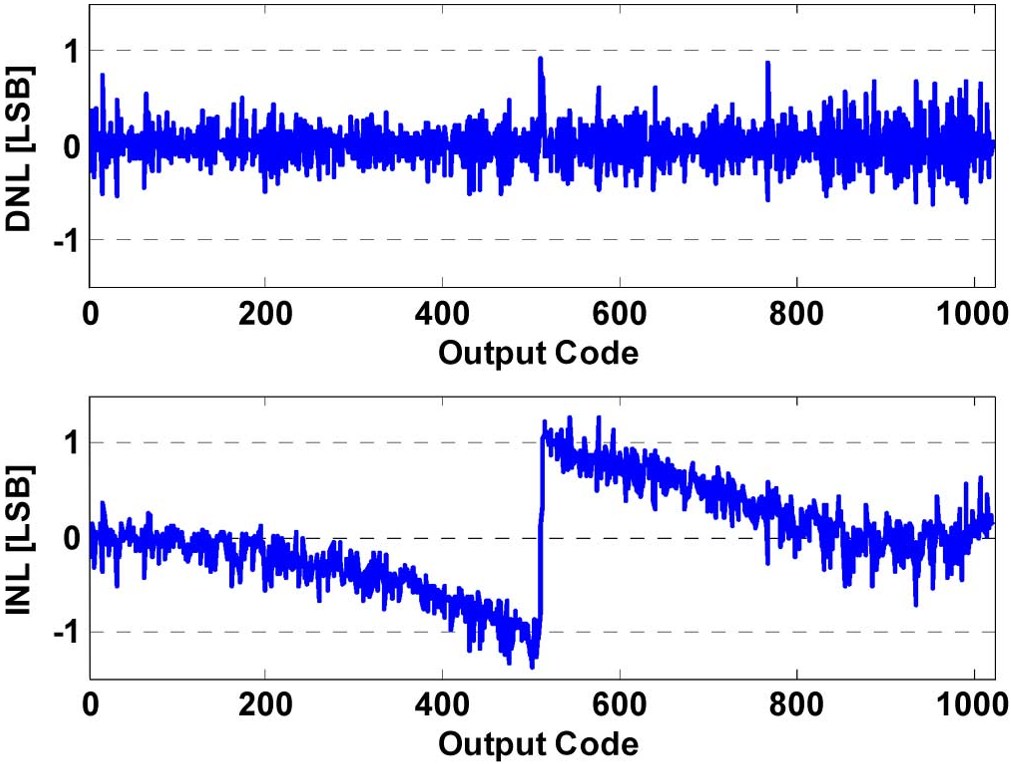

Fig. 14. Measured DNL and INL.

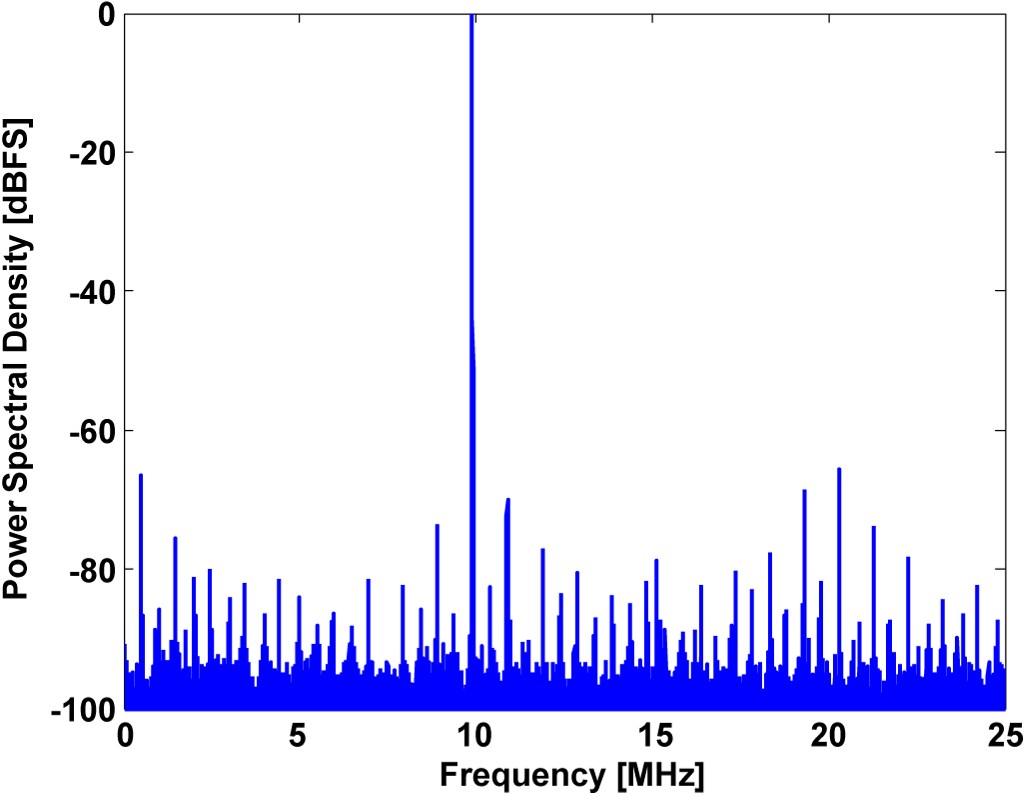

Fig. 15. Measured 32,768-point FFT spectrum at 50 MS/s.

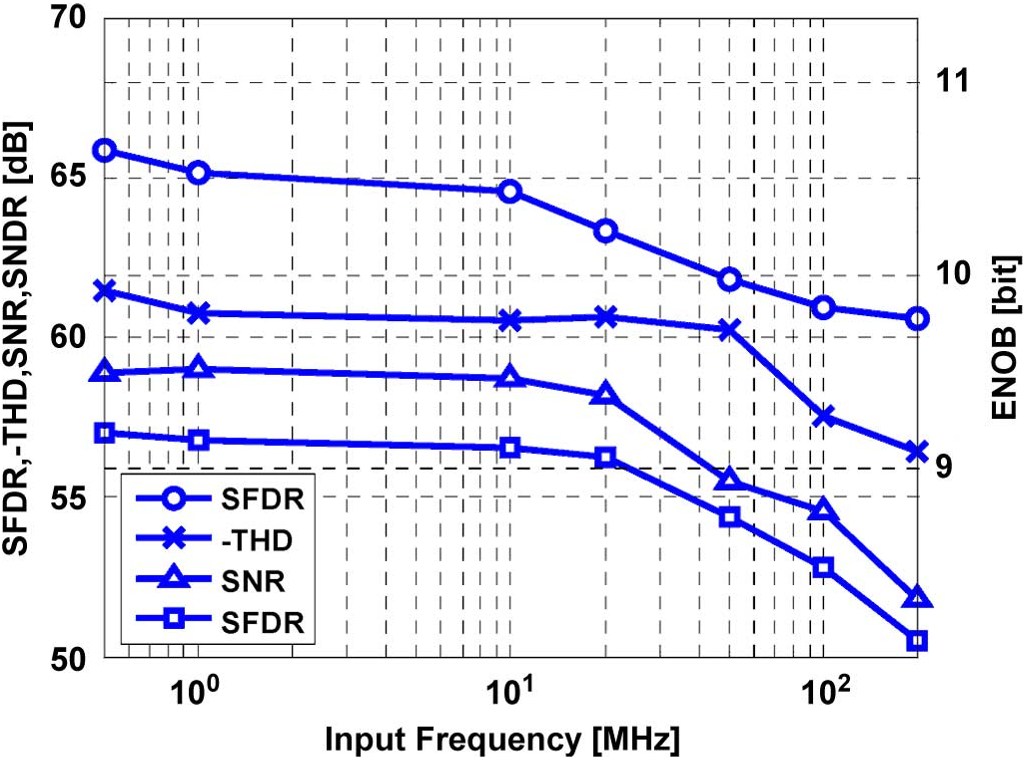

Fig. 16. Measured dynamic performance versus input frequency at 1.2 V and 50 MS/...

Paper Details

Title

A 10-bit 50-MS/s SAR ADC With a Monotonic Capacitor Switching Procedure

Published Date

Mar 24, 2010

Volume

45

Issue

4

Pages

731 - 740

TrendsPro

You’ll need to upgrade your plan to Pro

Looking to understand a paper’s academic impact over time?

- Scinapse’s Citation Trends graph enables the impact assessment of papers in adjacent fields.

- Assess paper quality within the same journal or volume, irrespective of the year or field, and track the changes in the attention a paper received over time.

Citation AnalysisPro

You’ll need to upgrade your plan to Pro

Looking to understand the true influence of a researcher’s work across journals & affiliations?

- Scinapse’s Top 10 Citation Journals & Affiliations graph reveals the quality and authenticity of citations received by a paper.

- Discover whether citations have been inflated due to self-citations, or if citations include institutional bias.